mirror of

https://github.com/rcore-os/rCore.git

synced 2024-11-25 01:16:18 +04:00

Rust version of THU uCore OS. Linux compatible.

1. Memory mapping at KSEG2_START(0xffff_fe80_0000_0000) will now be visible to all processes. This feature is required by Loadable Kernel Module when mapping kernel module into memory. 2. Wrapping PageTableImpl::active() into ManuallyDrop, so that no extra "mem::forget" is required. 3. Added PageTableImpl::kernel_table(). This function is the same as active() on x86_64, but not the same on aarch64. |

||

|---|---|---|

| bootloader | ||

| crate | ||

| docs | ||

| kernel | ||

| tests | ||

| tools | ||

| user@e493f65dfa | ||

| .gitignore | ||

| .gitmodules | ||

| .travis.yml | ||

| Cargo.toml | ||

| LICENSE | ||

| README.md | ||

| rust-toolchain | ||

rCore

Rust version of THU uCore OS Plus.

Going to be the next generation teaching operating system.

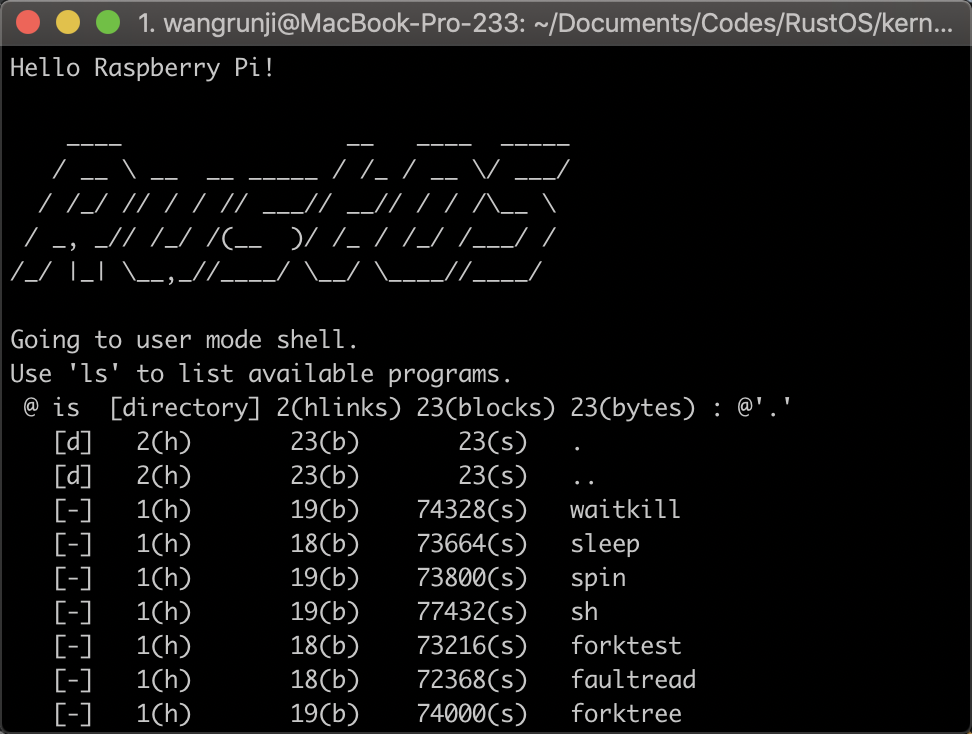

Supported architectures: x86_64, RISCV32/64, AArch64, MIPS32

Tested boards: QEMU, HiFive Unleashed, x86_64 PC (i5/i7), Raspberry Pi 3B+, Kendryte K210 and FPGA running Rocket Chip / TrivialMIPS

Building

Environment

- Rust toolchain at nightly-2019-03-05

- Cargo tools: cargo-xbuild

- QEMU >= 3.1.0

- bootimage (for x86_64)

- RISCV64 GNU toolchain (for riscv32/64)

- AArch64 GNU toolchain (for aarch64)

- musl-cross-make (for userland musl, or download prebuilt toolchain from musl.cc)

- libfuse-dev (for userland image generation)

See Travis script for details.

How to run

$ rustup component add rust-src llvm-tools-preview

$ cargo install cargo-binutils

$ cargo install cargo-xbuild --force

$ cargo install bootimage --version 0.5.7 --force

$ git clone https://github.com/rcore-os/rCore.git --recursive

$ cd rCore/user

$ make sfsimg arch={riscv32,riscv64,x86_64,aarch64,mipsel} # requires $(arch)-linux-musl-gcc

$ cd ../kernel

$ make run arch={riscv32,riscv64,x86_64,aarch64,mipsel} mode=release

$ make run arch=x86_64 mode=release pci_passthru=0000:00:00.1 # for ixgbe real nic, find its pci (bus, dev, func) first

Maintainers

| Module | Maintainer |

|---|---|

| x86_64 | @wangrunji0408 |

| RISC-V | @jiegec |

| ARM (Raspi3) | @equation314 |

| MIPS | @Harry_Chen @miskcoo |

| Memory, Process, File System | @wangrunji0408 |

| Network with drivers | @jiegec |

| GUI | @equation314 |

History

This is a project of THU courses:

- Operating System (2018 Spring)

- Comprehensive Experiment of Computer System (2018 Summer)

- Operating System Train (2018 Autumn)

- Operating System (2019 Spring)

Reports and Dev docs (in Chinese)

It's based on BlogOS , a demo project in the excellent tutorial Writing an OS in Rust (First Edition).

License

The source code is dual-licensed under MIT or the Apache License (Version 2.0).